# The Role of Hole Injection Layer in Enabling OLED Device Performance and Defect Tolerant Manufacturing

June 7<sup>th</sup>, 2011

"OLED Materials for Lighting and Displays"

A New Industrial Chemistry and Engineering (NIChE) Workshop by the Council for Chemical Research

### Key Facts:

- o Founded in 2002

- Based in Pittsburgh, PA USA

- Approximately 70 employees

- 190+ individual & pending patents worldwide

- Strategic investors:

### Business Model:

Develop and manufacture high-performance inks & leading-edge device technology for printed electronics

### Core Capabilities:

- Conductive polymer design and manufacturing

- Ink formulation, coating, and printing

- Printed device design & engineering

Dedication to Quality

ISO 9001 certified ISO 14001 compliant

No. 43632

### Plextronics Overview

### Target Markets:

### Existing Product Lines:

- <u>Plexcore® OC</u>: Conductive polymer inks for Hole Injection Layer (HIL) formation in OLED lighting and displays

- <u>Plexcore® PV</u>: OPV ink systems including matched Photoactive (p/n) and Hole Transport Layer (HTL) materials

- <u>Plexcore<sup>®</sup> OS</u>: P3HT polymer for OPV and OFETs

### New Product Lines:

- <u>Plexcore<sup>®</sup> HIL/HTL</u>: Ink system for printed OLED lighting and displays

- OPV Device Licensing: Printed solar devices incorporating Plexcore<sup>®</sup> PV inks specially designed for use with indoor, artificial lighting

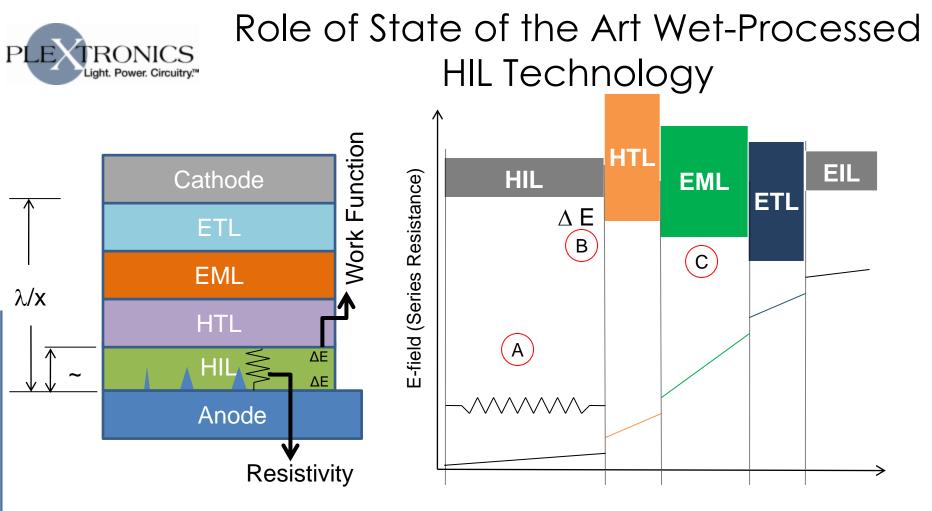

- Minimize energy barriers at anode and HTL interfaces

- Minimize voltage penalty as a f(thickness)

- Facilitate freedom in optical cavity design

- Passivation of defects on electrode surface

### Outline

Overview of Plexcore OC Technology

- High performance OLED stacks using Plexcore OC

- Display

- Lighting

• 150 x 150 mm coating capability at Plexcore OC

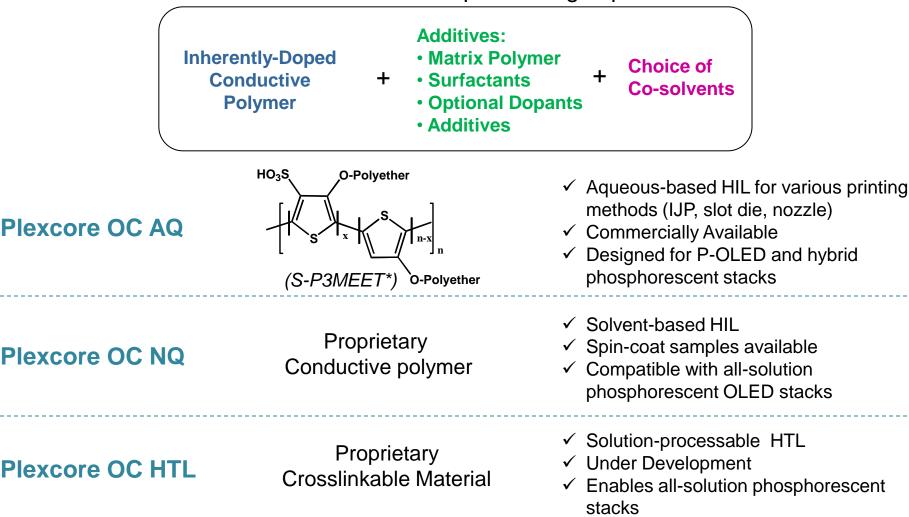

# Plexcore OC Product Lines

Combining conducting polymer chemistry with ink formulation & processing expertise

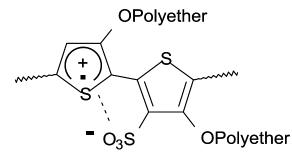

\* Sulfonated poly(thiophene-3-[2-(2-methoxyethoxy)ethoxy]-2,5-diyl) (S-P3MEET)

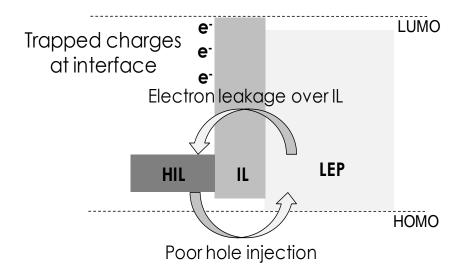

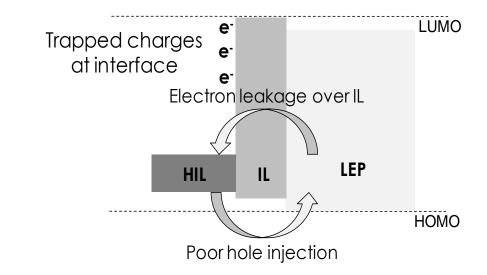

# Plexcore<sup>®</sup> OC is Resistant to De-doping Phenomena

see also de Kok, M. M. et al Physics of Organic Semiconductors, Wiley-VCH, Edt. Brutting, W., 451-470

# Plexcore<sup>®</sup> OC is Resistant to De-doping Phenomena

see also de Kok, M. M. et al Physics of Organic Semiconductors, Wiley-VCH, Edt. Brutting, W., 451-470

# Plexcore<sup>®</sup> OC is Resistant to De-doping Phenomena

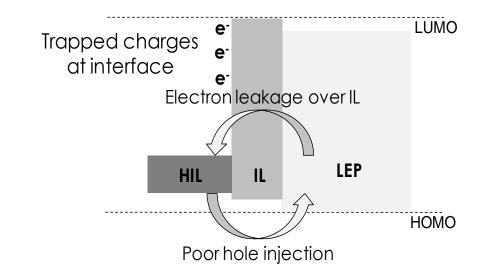

Exposure to electron current for some aqueous solution processed HIL/HTL materials can lead to operational performance degradation via dedoping phenomena

see also de Kok, M. M. et al Physics of Organic Semiconductors, Wiley-VCH, Edt. Brutting, W., 451-470

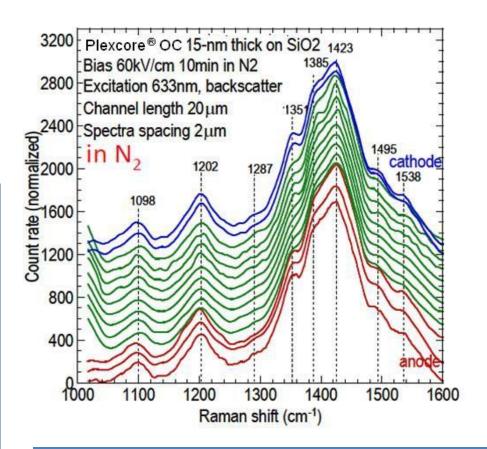

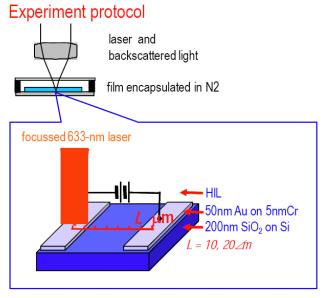

# Micro-Raman Supports Absence of Dedoping

Measured on InVia Renishaw Raman microscope with HeNe 633nm laser focussed through a x20 (NA0.75) objective and at a power that does not cause laser-induced damage as verified by repeated measurements at the same spot. All samples were encapsulated in N2 before Raman measurements to prevent photo-oxidation during measurement. No bias was applied during measurement.

In N<sub>2</sub> and air up to 60 kV (120V), there is no evidence of electricallyinduced change in the doping-level of Plexcore<sup>®</sup> OC

see also, Ho, P. K-H. Adv. Materials 2007, 19, 4202

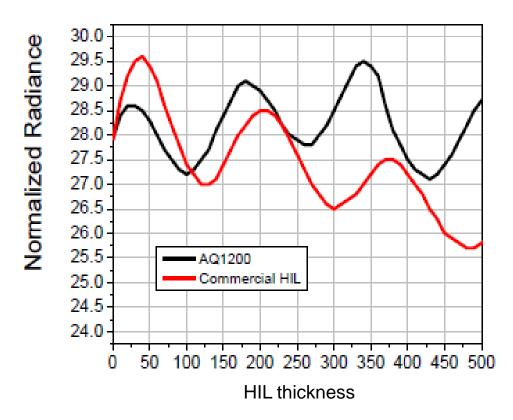

### Using AQ HIL for Optical Cavity Tuning

- Simulation results show higher light out-coupling at higher HIL thickness

- Potential to further increase the allowed thickness to facilitate planarization

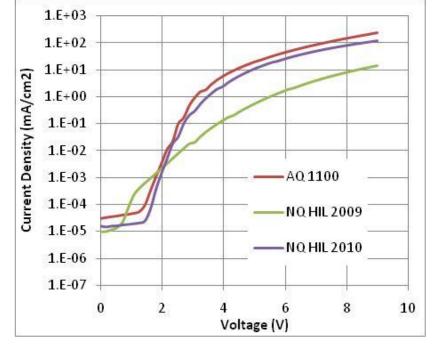

### New Development: Improving Hole Injection Capability of Non-Aqueous HIL

#### **Design Rules**

No protons

$\rightarrow$  No water or protic solvents

High Transparency

Planarization

#### **Performance Benefits:**

- Eliminate degradation mechanisms

- Enable higher performing phosphorescent devices

New Non-Aqueous HIL delivers comparable hole injection to Aqueous HIL

### HIL For Lighting

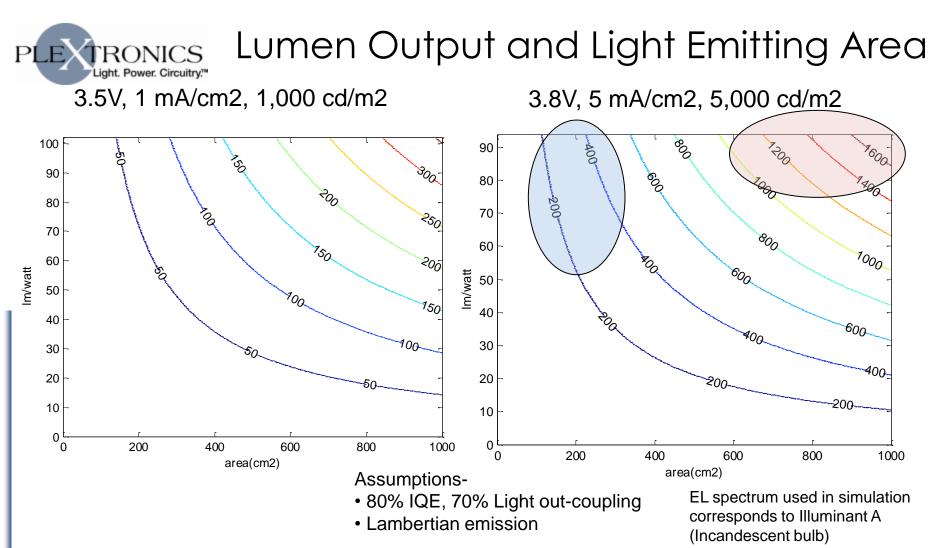

- At a brightness of 1,000 cd/m2 lumen output is limited

- At 3,000 to 5,000 cd/m2 lumen output enables different applications for reasonable dimensions of panels

- There are two areas a) operating voltage to maximize light output and b) practical limit of production panel area where HIL can play a role

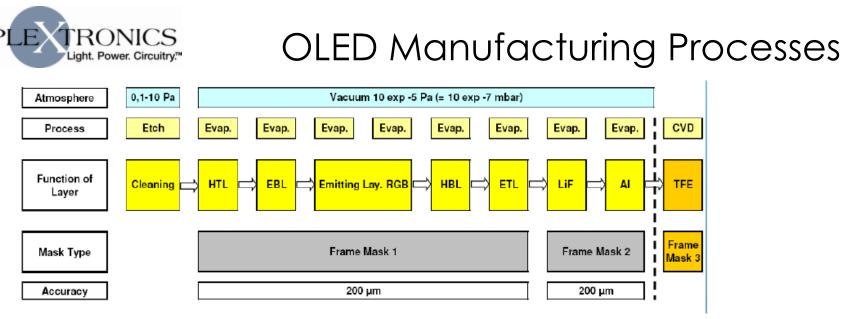

Example of OLED Fab line, Applied Materials

- Pilot lines with select device architectures, materials sets and equipment are being set up

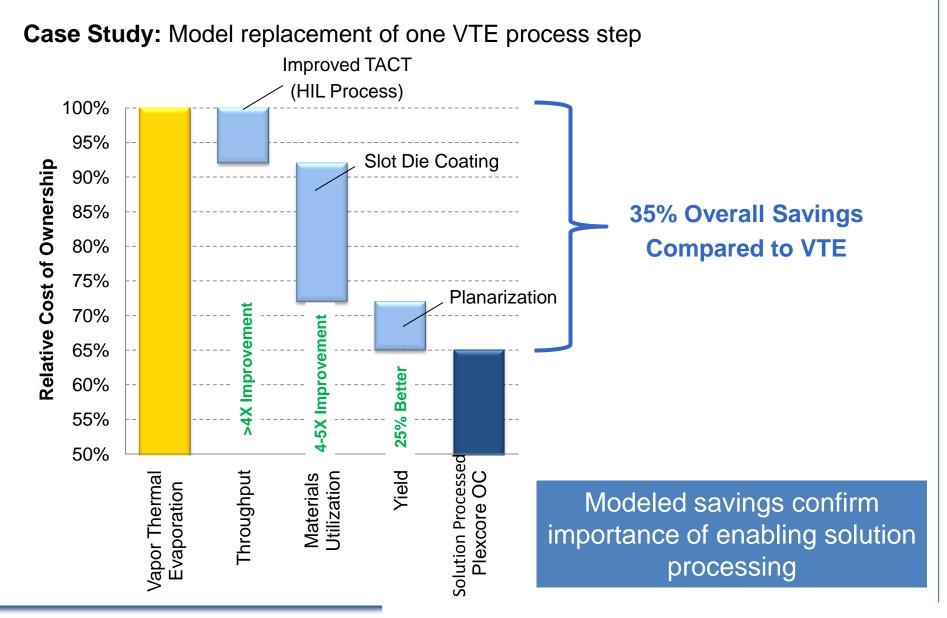

- Opportunity exists to lower costs of panels via demonstration of improvement in specific unit operations

- Demonstrate better materials utilization

- Lower cycle time

- Demonstrate improved yield

# Why focus on HIL?

### Use of p-doped Hole Injection Layer (HIL) in OLED SSL Device Stacks

`RONICS

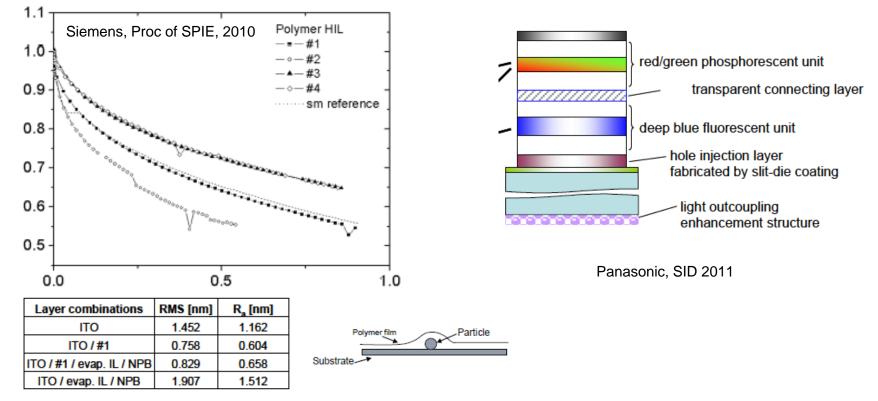

- High performance 'hybrid devices' that incorporate solution based HIL and vapor organic layers are becoming more common

- The use of solution based HIL offers added advantages for manufacturing that go beyond device stack development for efficacy and lifetime

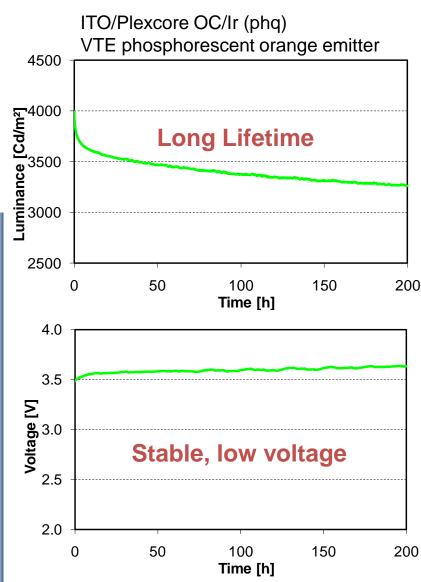

### Long lifetime and low voltage in Hybrid phosphorescent SMOLED Device

RONI

t. Power. Circuitry.

| Performance Metric        | Value        |

|---------------------------|--------------|

| Voltage                   | 3.1 V        |

| EQE                       | 7.3          |

| Cd/A                      | 12.9 Cd/A    |

| Lm/W                      | 12.9         |

| Lifetime (T75, 4000 nits) | 1,145 hrs    |

| Lifetime (T50, 1000 nits) | 107,000 hrs* |

Solution processed Plexcore OC in a vapor deposited stack exhibits excellent lifetime coupled with voltage stability

Yield Improvement is driver for Large-Area Manufacturing

### Guidance for Materials Development-Device

| Variable                                                | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface energy offsets                                | Achievement of a flat band device architecture with attention paid to processes that create the final interface                                                                                                                                                                                                                                                                              |

| Mobility within OLED device layers                      | Maximizing mobility helps in bringing down voltage<br>once interfaces are dealt with. This can also facilitate<br>increasing the thickness of the layers. Materials<br>design that facilitate improved charge transport (<br>sensitive to deposition process variables for wet<br>processing) is key here.                                                                                   |

| Impact of Charge Trapping<br>and Interfaces on lifetime | Materials need to be designed to be robust to charge<br>trapping phenomena which are an essential element<br>of mechanism for light emission in the emissive layer.<br>Design of architectures should facilitate minimization<br>of charge accumulation at interfaces. Simpler device<br>architectures minimize the number of interfaces but<br>are also susceptible to more charge trapping |

### Process Development- Organic Layer Deposition

| Work<br>Package                                       | Package Classification                    | Tasks to Monitor                                                                                                                     |

|-------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Process<br>development<br>for thin film<br>deposition | Processability- Air/Dry<br>Air/Inert      | Environment for coating and for drying                                                                                               |

|                                                       | Tool + Ink evaluation                     | Coating speed, thickness uniformity, process<br>package for production environment, duration<br>of operation/uptime in coating trial |

|                                                       | Film coating evaluation                   | Film uniformity, wetting on backplane features                                                                                       |

|                                                       | Patterned deposition                      | Tolerance for film edge alignment with<br>backplane features                                                                         |

|                                                       | Film drying                               | Drying method, number of ovens,<br>environment, anneal time, solvent stripping                                                       |

|                                                       | Time/Environment<br>between coating steps | Substrate handling requirements, variation & tolerance to variation in queue time windows, ability to store film coated substrates   |

Shape generation

Cleaned/ Patterned surface

Edge Definition  $\leftarrow$

## Materials & Translation to Panels

RONICS

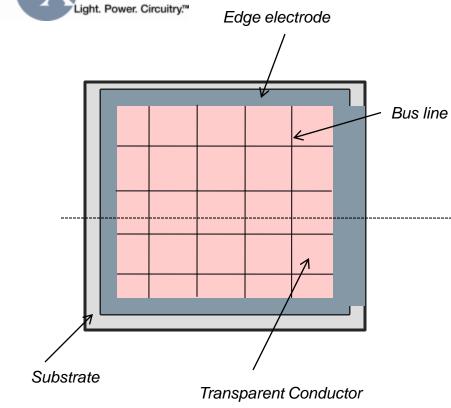

Need to improve thermal management for higher current

- Reduce non uniform degradation due to thermal effects

- Reduce pathways for leakage current

- Address tradeoff between the illuminated area of the panel and thermal management strategies such as bus lines

Materials & Device Architecture Development to increase current at given voltage

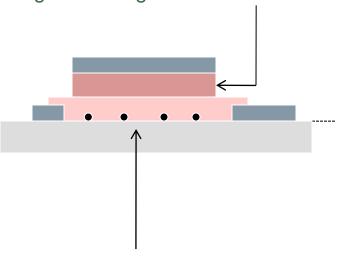

**Deposition of layers**

- Multiple surface types exist during coating events

- Thin film coatings need to maximize materials usage

- Solvent selection to facilitate fast drying times

### Guidance for Materials Development-Panel

| Variable                                                                    | Description                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sensitivity of materials to handling environment                            | Ability to improve process throughput is key. This is defined on<br>the basis of a) robustness to moisture/oxygen/light b) solvent<br>removal conditions for wet processed layers c) base purity of<br>materials and solvents                                                                                               |

| Device performance<br>tolerance to thickness<br>uniformity over large areas | Scaling materials demonstrated to perform in lab devices to<br>large are substrates requires the use of deposition techniques<br>that will not easily lend themselves to maintaining thickness<br>uniformity for 10nm films. Hence demonstration of low<br>sensitivity of operating voltage to layer thickness is essential |

| Scalability of material synthetic procedures                                | Minimize number of synthetic steps. Ensure robustness of procedure to factors that compromise purity                                                                                                                                                                                                                        |

| Thermal Effects                                                             | Materials and processes that eliminate volatiles are essential.<br>Low cost solutions to manage thermal non-uniformities are<br>key. Minimization of ohmic losses via selection of materials<br>and panel design will help facilitate minimization of non<br>uniformities in device degradation                             |

### Leveraging Available US-based Assets for Ink & Process Development

- We utilize the D-Line to evaluate our materials using manufacturing-worthy processes and equipment.

- Specifically, we are:

- Developing inks for large area blanket coating

- Evaluating encapsulation technologies to understand interactions within the device

- Testing alternative cathode and device architectures

- Implementing new module designs

٠

•

٠

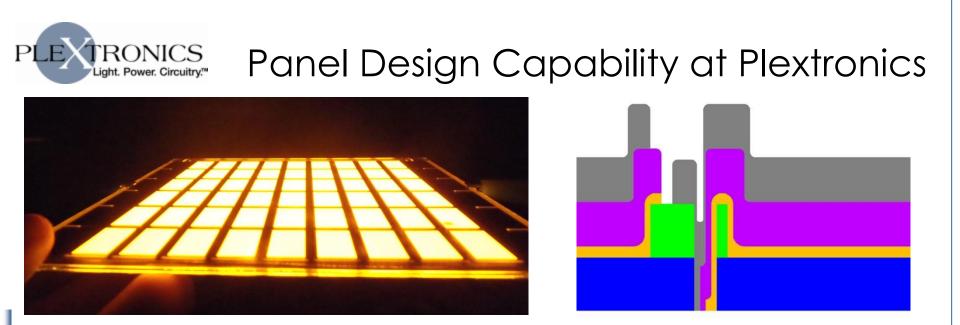

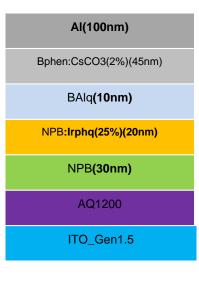

- 6"X6" Orange PHOLED panel fabricated at R&D line

- Uses a 9s6p substrate design

- Uses Plexcore AQ 1200 and orange vapor PHOLED

- HIL in this case was spin coated

#### **Plextronics Confidential**

### Summary

- Plexcore<sup>®</sup> OC is a High-Performing HIL with excellent stability to dedoping phenomena

- ✓ Low cost, scaled solution processing is key to OLED commercialization

- Tunability of HIL can modulate charge injection to optimize device stack performance

- Proven device performance with Plexcore<sup>®</sup> OC has been demonstrated across emitter platforms and technologies; shows potential for dramatic reduction in cost-of-ownership compared to vapor thermal evaporation

2180 William Pitt Way | Pittsburgh, PA 15238 | www.plextronics.com | (412) 423-2030

# Thank You

### Mathew Mathai, PhD

Director, Lighting mmathai@plextronics.com

Ink Sales/Info: Mary Boone, mboone@plextronics.com R&D volumes of select products also available through: <u>www.aldrich.com</u>